Parametry

- 199 stránek

- 7 hodin čtení

Více o knize

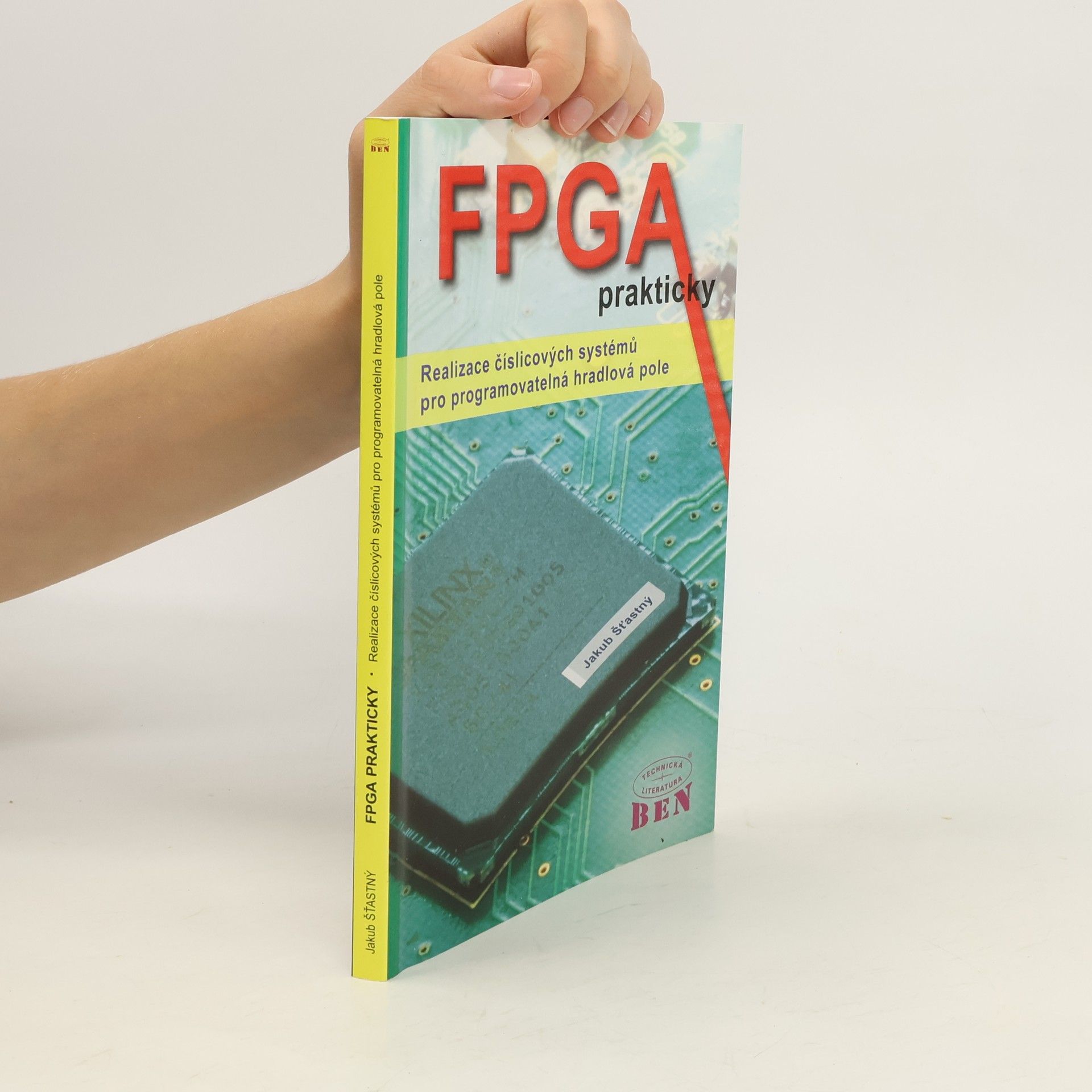

Tato publikace vyplňuje mezeru na českém knižním trhu tím, že se zaměřuje na praktické aspekty návrhu číslicových systémů. Místo popisu jazyka VHDL se soustředí na obvodovou realizaci, správné použití návrhového softwaru a varuje před nástrahami, s nimiž se mohou setkat jak začátečníci, tak pokročilí návrháři. Obsahuje témata, která jsou v české literatuře málo diskutována, ale jsou klíčová pro úspěšný návrh. Každé téma je doplněno ukázkovými příklady a cvičeními pro lepší pochopení. Publikace pokrývá základní postupy návrhu obvodů, moderní software, programovatelná hradlová pole, architektury a kritéria pro výběr obvodů. Dále shrnuje konstrukce jazyka VHDL, systémový návrh obvodů, aritmetické operátory, datové cesty a obvody pro zpracování signálů. Obsahuje také kapitolu o stavových automatech, pamětích, hodinách, resetu a asynchronních signálech. Na závěr se zaměřuje na rozdíly mezi návrhem FPGA obvodů a zákaznických integrovaných obvodů. Publikace je určena studentům, pedagogům a odborníkům, ale také domácím kutilům, kteří chtějí využít programovatelná hradlová pole.

Nákup knihy

FPGA prakticky, Jakub Šťastný

- Jazyk

- Rok vydání

- 2011

- product-detail.submit-box.info.binding

- (měkká)

Doručení

Platební metody

Nikdo zatím neohodnotil.